AlteraのFPGA・CPLDを開発する時には、IDE (Integrated Development Environment) であるQuartus Ⅱを利用しています。

このIDE、何も設定せずにTiming Analysisをすると、clock周波数を1GHzとして解析してしまうようです。

別にそれでもよいのですが、"Timing requirements not met"とエラーが出ているのは精神的によくないので、clockに適切な周波数を設定します。

その方法なのですが、"quartus ii set clock frequency"で調べてもあまり出てこなかったので、記しておきます。

(この検索ワードだと、実際に水晶振動子などから与える源clockの周波数の決め方みたいですが、Timing Analysisのための設定方法です。)

参考サイト

…と思っていたのですけれど、"SDC Altera"とかで調べたら出てくるみたいですね。

Quartus II はじめてガイド - タイミング制約の簡易設定方法 ~ TimeQuest Timing Analyzer Wizard ~ ver.10.0

https://www.altima.jp/members/japanese/download/tqwzd_v10_01.pdf

上のAltima社のはじめてガイドは、日本語でQuartus IIの使い方が一通り載っているので良さそうです。この記事の意味…。

インテル® FPGA : ソフトウェアに関する日本語資料

Quartus II TimeQuest タイミング・アナライザ・クックブック

https://www.altera.co.jp/ja_JP/pdfs/literature/manual/mnl_timequest_cookbook_j.pdf

設定方法

TimeQuestに渡すであろう.sdcファイルに記述するのが要なのでしょうが、GUIで行きます。

DE0のためにQuartus II 64-bit v13.0を使っているので、古いですけれどこれで説明します。

まず、何も設定せずにTiming Analysisをします。

module唯一のclockであるI_SYSCLKに、1000MHzが与えられています。

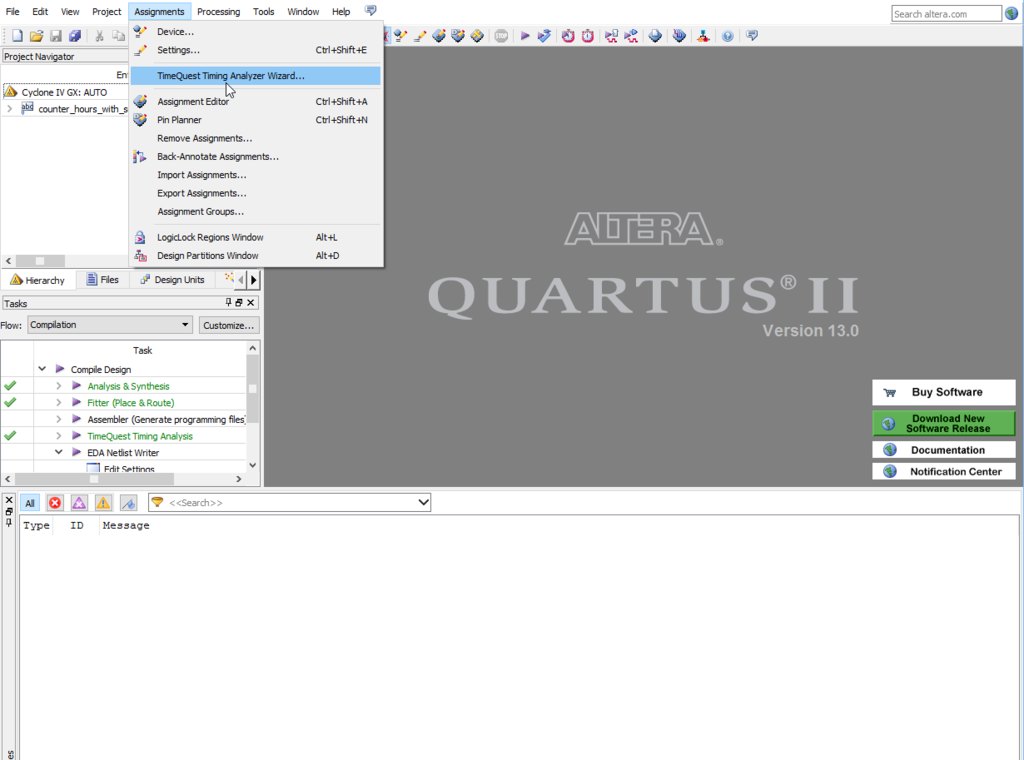

次に、周波数を設定します。メニューの[Assignments] -> [TimeQuest Timing Analyzer Wizard]を選びます。

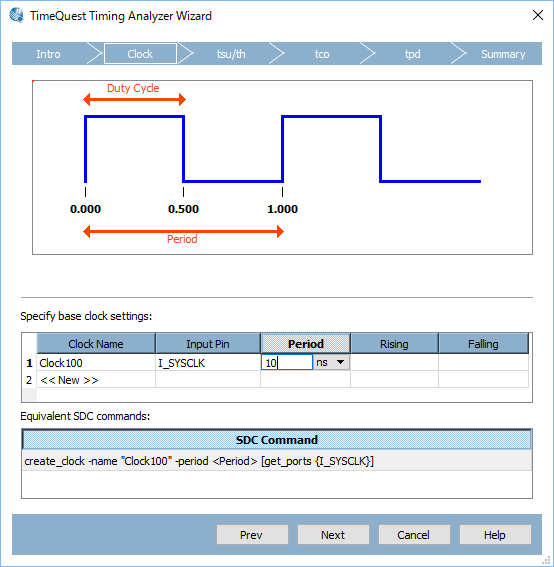

最初の画面はNextで飛ばします。2つめの画面が、clockを与える設定を行う画面です。

ここでは、f = 100[MHz]のclockを与える設定にします。周期Tは、T = 1/f = 10[ns]です。

まず、[Clock Name]には適当な名前を与えます。

次に、[Input pin]には、このclockを与える信号名(?)を与えます。今回はI_SYSCLKです。

最後に、[Period]に周期10[ns]を与えます。[Rising]と[Falling]は空欄でもよく、その場合duty比50%のclockとなるようです。

その後[Next]を押して、最後の画面ではファイル名を確認して[Finish]です。

今回は、"dummy_1.sdc"という.sdcファイルが生成されました。中身は以下のようなテキストが記されたファイルです。

これで再びTiming Analysisをしてみました。

ちゃんと周波数が100[MHz]になっていました。

さっきの.sdcファイルが読み込まれているようです。